Pentium CPU

Pentium CPU |

![]() Intel Pentium CPU

Intel Pentium CPU

S Intel i80486 CPU inštrukčne kompatibilný.

Zdvojený 5-úrovňový superskalár s 8-úrovňovou zreťazenou FPU (Floating Point

Unit).

Multiprocesorová podpora.

Kontrola parity na zberniciach.

Predikcia vetvenia, pamäť cieľových adries skokov -(BTB Branch Target Buffer).

· 8 kbytová inštrukčná cache

· 8 kbytová dátová cache (Harvardská architektúra)

obidve s 2 asociatívnymi sekciami, spätným zápisom.

· 32 bitová interná dátová zbernica (CPU - MMU (Memory Management Unit, vložená

cache))

· 64 bitová externá dátová zbernica (MMU, vložená cache))

· 32 bitová adresová zbernica

Púzdro: 296 vývodov PGA (Pin Grid Array)

Všetky Intel Pentium CPU vyrobené pred novembrom 1994 vykazovali chybu, ktorá bola

prezentovaná pri delení v FPU. Chyba sa prejavovala ako nesprávna hodnota po delení.

Popiska na CPU:

· typ CPU, takt

· A80502133: 133 MHz Pentium

· krok a kvalita

· SY022/SSS:

· SY022: číslo litografickej masky,

· s-spec (charakteristika): SK, SU, SX, SY, SZ,

· S: štandardné napájanie (3.135 - 3.6 V), V (VRE): narrowed voltages 3.4 - 3.6

V,

· S: štandardné časovanie, M: Minimum Valid MD timing,

· S: štandardná konfigurácia, U: Uniprocessor,

· iPP mark: na všetkých Pentium CPU od 90 MHz a rýchlejších, 75 MHz Pentium CPU

majú len i75, 90 MHz a rýchlejšie CPU s i75 môžu byť falošné,

· iCOMP index,

· sériové číslo,

· 6044482-0591: číslo a sériové číslo,

· krajina výrobcu,

· MALAY: Malayasia.

![]() Intel Pentium P5 CPU

Intel Pentium P5 CPU

Marec 1993

60 MHz (Intel Pentium 60 CPU): 5 V, iCOMP 510

66 MHz (Intel Pentium 66 CPU): 5 V, iCOMP 567

(Prvé 66 MHz CPU mali teplotné problémy a boli uvádzané ako 60 MHz verzie CPU).

Technológia: 0.8 mm biCMOS

Integrácia: 3 200 000 tranzistorov

ID:

krok úrovne Ax: DH = 0x05 (ID druhu), DL = 0x0X (ID modelu, revízia)

krok úrovne B1: DH = 0x05 (ID druhu), DL = 0x13 (ID modelu, revízia)

krok úrovne C1: DH = 0x05 (ID druhu), DL = 0x15 (ID modelu, revízia)

krok úrovne D1: DH = 0x05 (ID druhu), DL = 0x17 (ID modelu, revízia)

CPUID: krok úrovne Ax: DH =druh = 0x5, model = 0

krok úrovne Bx: DH =druh = 0x5, model = 1

Púzdro: 273 vývod�����������������������������������������������������������������������������������������������ov PGA (Pin Grid Array) (Socket 4: 273 vývodov, 5 V).

Model 1, revízia 7: chyba FDIV opravená.

60 MHz: 80500

60, 66 MHz: 80501

![]() Intel Pentium P54C CPU

Intel Pentium P54C CPU

Upgrading: Intel Pentium P54M Overdrive (2 CPU spolupracujú).

Intel Pentium P55CT CPU

1994

50/75 MHz (Intel Pentium 75 CPU) (notebooky, P54T): 3 V, iCOMP 610

60/90 MHz (Intel Pentium 90 CPU): 3.3 V, iCOMP 735

66/100 MHz (Intel Pentium 100 CPU): 3.3 V, iCOMP 815

Technológia: 4 vrstvy kovu, 0.6 mm biCMOS

Integrácia: 3 300 000 tranzistorov

Púzdro: 296 vývodov PGA (Pin Grid Array) (Socket 5: 320 pins, 3.3 V).

60/120 MHz (Intel Pentium 120 CPU, Intel Pentium P54CQS CPU) 3.3 V, marec 1995, iCOMP

1000,

krok úrovne C2.

Technológia: 0.35 mm CMOS.

Integrácia: 3 100 000 tranzistorov

Púzdro: 296 vývodov PGA (Pin Grid Array) (Socket 5).

![]() Intel Pentium P54CS

CPU.

Intel Pentium P54CS

CPU.

66/133 MHz (Intel Pentium 133 CPU): iCOMP 1110

Púzdro: 296 vývodov PGA (Pin Grid Array) (Socket 5),

60/150 MHz: 3.3 V, iCOMP 1195

66/166 MHz: 3.3 V, iCOMP 1340

66/200 MHz: 3.3 V

Púzdro: 296 vývodov PGA (Pin Grid Array) (Socket 7: 321 pins, 3.3 V, maximum 5 A,

maximum 17 W).

Technológia: 0.35 mm CMOS.

Integrácia: 3 100 000 tranzistorov.

Násobiteľ: 1.5, 2, 2.5, alebo 3.

ID:

krok úrovne A: DH = 0x05 (ID druhu), DL = 0x2X (ID modelu, revízia)

krok úrovne B1: DH = 0x05 (ID druhu), DL = 0x21 (ID modelu, revízia)

krok úrovne B3: DH = 0x05 (ID druhu), DL = 0x22 (ID modelu, revízia)

krok úrovne B5: DH = 0x05 (ID druhu), DL = 0x24 (ID modelu, revízia)

krok úrovne C1: DH = 0x05 (ID druhu), DL = 0x25 (ID modelu, revízia)

krok úrovne C2 (120 MHz): DH = 0x05 (ID druhu), DL = 0x25 (ID modelu, revízia)

· P54CQS, 120 MHz: DH = 0x05 (ID druhu), DL = 0x25 (ID modelu, revízia)

· P54LM, 2.9 V, krok úrovne Ax: DH = 0x05 (ID druhu), DL = 0x25 (ID modelu, revízia)

CPUID: druh = 0x5, model = 0x2.

Model 2, revízia 5: chyba FDIV opravená.

60, 66 MHz: 80501

50/75, 60/90, 66/100, 60/120, 66/133 MHz: 80502

![]() Intel Pentium P54M

CPU

Intel Pentium P54M

CPU

Overdrive pre Intel Pentium P54C CPU.

Technológia: CMOS

ID: DH = 0x25 (ID druhu), DL = 0x2X (ID modelu, revízia)

![]() Intel Pentium OverDrive

CPU

Intel Pentium OverDrive

CPU

Pentium OverDrive pre Intel Pentium P5 CPU.

60/120 a 66/133 MHz (P5T, PODP5V120/133): pre 60 a 66 MHz systémy, iCOMP 877/978

3.3 V core (voltage regulator), I/O znáša 5V.

Púzdro: 273 vývodov PGA (Pin Grid Array) (Socket 4).

Technológia: 0.8 mm CMOS.

Integrácia: 3 100 000 tranzistorov.

Pentium P54CT(A) OverDrive processor pre Intel Pentium P54C CPU.

50/125 MHz (PODP3V125): pre 50/75 MHz systémy, iCOMP 1070

60/150 MHz (PODP3V150): pre 60/90 MHz systémy, iCOMP 1176

66/166 MHz (PODP3V166): pre 66/100 MHz systémy, iCOMP 1308

Napájanie: 3.3 V: 3.135 - 3.600 V.

Púzdro: 320 vývodov PGA (Pin Grid Array) (Socket 5/7).

Technológia: 0.35 mm CMOS.

Integrácia: 3 100 000 tranzistorov.

![]() AMD K5 CPU (K86

series)

AMD K5 CPU (K86

series)

S Intel Pentium CPU kompatibilný.

Preklad operacií X86 na RISC (ROP).

Superskalár: 5 úrovňový

3 celočíselné zreťazenia

1 FP zreťazené spracovanie

8 kbytová dátová cache (Harvardská architektúra)

protokol MESI (modified, exclusive, shared, invalid)

blokovo orientovaný, predikcia vetvenia, špekulatívne vykonávanie.

Púzdro: 296 vývodov SPGA (Socket 7)

Technológia: 3 vrstvy, 0.5 mm CMOS

0.35 mm CMOS (prvý štvrťrok 1996)

ID reťazec: “AuthenticAMD“

AMD 5k86 K5 CPU (K86 series)

AMD K5-PR75 CPU (SSA, model 0): 50/75 MHz, marec 1996

AMD K5-PR90 CPU (SSA, model 0): 60/90 MHz

AMD K5-PR100 CPU (SSA, model 0): 66/100 MHz

AMD K5-PR120 CPU (5k86, model 1): 60/90 MHz

AMD K5-PR133 CPU (5k86, model 1): 66/100 MHz

AMD K5-PR150 CPU (5k86, model 2): 60/105 MHz

AMD K5-PR166 CPU (5k86, model 2): 66/116 MHz, marec 1997

AMD K5-PR166 CPU (5k86, model 3): 66/133 MHz

Produkcia ukoncená v polovici roku 1997.

3.52 V.

Technológia: 0.35 mm.

Integrácia: 4 300 000 tranzistorov.

Násobiteľ nemožno meniť.

AMD 5k86 SSA/5 CPU (séria K86)

Predverzia AMD 5k86 K5 CPU:

veľa interných čakaní

neúplná pamäť cieľových adries skokov BTB (Branch Target Buffer)

Vlastnosti:

VME

I/O Breakpoints

TSC (Time Stamp Counter)

Machine Check

133 MHz: máj 1996

Krok úrovne: 0x50

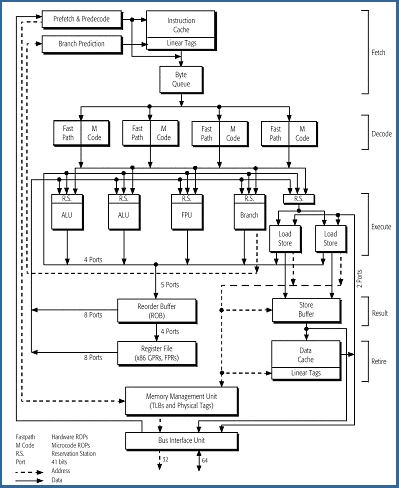

- Bloková schéma K5

![]() Cyrix 586 CPU

Cyrix 586 CPU

S Intel Pentium CPU kompatibilný. Hodiny zdvojené alebo strojené.

16 kbytová unifikovaná cache: 4 asociatívne sekcie

spätný zápis

Management napájania:

SMM (System Management Mode)

hardware suspend,

stop-clock,

FPU auto-idle.

50 MHz

100 MHz

120 MHz

3.3 V, 5 V I/O

Superskalár: zdvojený 7 úrovňový

predikcia vetvenia, pamäť cieľových adries skokov

FPU: 4x64 bitové zápisové bufre

Púzdro: 296 vývodov PGA

Technológia: 0.5 mm CMOS (IBM, SGS-Thomson)

ID reťazec: "CyrixInstead"

DIR0 register: 0x30.

![]() Cyrix M1 CPU

Cyrix M1 CPU

Cyrix 5x86 CPU

Primárna cache: 16 kbyte unifikovaná, spätný zápis, 4 asociatívne

sekcie.

2x, 3x clock násobička.

Management napájania:

SMM (System Management Mode),

hardware suspend, stop clock,

FPU auto-idle.

50/100, 33/100 (Cyrix Cx5x86-100GP/QP CPU): 3.45 V, júl 1995

40/120 (Cyrix Cx5x86-120GP/QP CPU): 3.45 V

Násobiteľ: 2 alebo 3

V praktických testoch bežných aplikácií je rýchlejší ako Intel Pentium Pro (Cyrix

optimalizoval CPU pre 16 bit kód, Intel pre 32 bit kód).

Púzdro:

168 vývodov PGA (Pin Grid Array) (GP),

208 pin QFP (Quad Flat Package) (QP).

![]() NexGen Nx586/Nx587 CPU

chipset

NexGen Nx586/Nx587 CPU

chipset

S Intel Pentium CPU inštrukčne kompatibilný. Bez FPU. RISC (Reduced Instruction Set

Computer): RISC86 Inštrukčná sada Intel Pentium CPU.

Vnútorne napätie 4 V.

· 16 kbytová inštrukčná cache

· 16 kbytová dátová cache (Harvardská architektúra)

Radič externej L2 cache pre 256 kbytov alebo 1 Mbyt je integrovaný na čipe.

Marec 1994

NexGen Nx586 CPU: 60 MHz: 4V

66 MHz: 4V

NexGen Nx587 NPX: 60 MHz: 4V

66 MHz: 4V

NexGen NxVL Vesa Local Bus interface: 60 MHz

66 MHz

NexGen NxPCI PCI Bus interface: október 1995

Superskalár: 2 celočíselné jednotky

FP sčítačka (2 cykly)

FP násobička (2 cykly)

P��������������������������������������������������������������������������������������������������������redikcia vetvenia

NexGen Nx586 CPU: 4 V, 9 W, 3 500 000 tranzistorov, 0.5 mm CMOS

NexGen Nx587 NPX: 4 V, 1.1 W, 700 000 tranzistorov, 0.5 mm CMOS

NexGen NxVL Vesa Local Bus interface: 5 V, 1 W, 0.5 mm CMOS

September 1994

70 MHz: (PR 75)

80 MHz

90 MHz

100 MHz

December 1994

133 MHz

Technológia: 0.5 mm CMOS

Výrobca IBM.

Intel Pentium Pro P6 CPU |

Kompatibilný s predošlými iapx CPU (RISC s X86 prekladom).

Superzreťazený Superskalár:

3 celočíselné jednotky,

12 úrovní,

instruction pool,

fetch/decode unit,

jednotka prideľovania mikrokódu a výkonu inštrukcií (2 AGU (Address Generation Unit):

1 load,

1 store,

1 JEU (Jump Execution Unit),

2 IEU (Integer Execution Unit),

1 FEU (Floating Execution Unit)),

jednotka odsunu.

ECC (Error Correcting Code).

Analýza chýb / obnovenie.

Kontrola funkčnej redundancie.

Viacnásobná predikcia vetvenia, analýza toku dát, špekulatívne vykonávanie.

L1 a L2 na čipe.

Level 1 cache: 8 kbyte pre inštrukcie,

8 kbyte pre data (Harvardská architektúra).

Level 2 cache: 256/512 kbyte alebo 1 Mbyte,

MESI architektúra, 4 Gbyte cachovateľnej main pamäti.

Podpora Multi-procesorového systému.

2 alebo 4 Intel Pentium Pro CPU môžu spolupracovať v SMP (Symmetric Multi-Processor)

základe.

Zvýšenie rýchlosti 2-CPU konfigurácie je výborné. 4-CPU konfigurácia je relatívna

zlá.

60/120 MHz

66/133 MHz (engineering sample): 256 kbyte L2 cache, 2.9 V, 3.1 V, 14 W

60/150 MHz: 256 kbyte L2 cache, 3.1 V, november 1995, 23.0 W

Technológia: 0.6 mm biCMOS, prebíjacia domino logika.

Integrácia: 5 500 000 tranzistorov.

66/166 MHz: 512 kbyte L2 cache, november 1995, 27.5 W

60/180 MHz: 256 kbyte L2 cache, november 1995, 24.8 W

66/200 MHz: 256 kbyte L2 cache, 3.3/3.5 V, november 1995, 27.3 W

66/200 MHz: 512 kbyte L2 cache, november 1995, 32.6 W, 0.35 mm technológia

Napájanie: 3.3 V.

Púzdro: 387 pin CPGA (Ceramic Pin Grid Array) (Socket 8).

Procesor a L2 cache su spojené DIB (Dual Independent Bus).

Technológia: 0.35 mm CMOS.

Integrácia: 5 500 000 tranzistorov.

ID: DH = 0x06 (model ID, family ID), DL = 0xXX (revision).

Pentium Pro a Pentium II procesory obsahovali chybu FPU (Floating Point Unit). Konverzia

veľkých záporných čísel na integers bola občas chybná a vyhlasovala

pretečenie.

66/200 MHz: 1 Mbyte L2 cache, 3.3 V, august 1997, 43 W

66/200 MHz: 1 Mbyte L2 cache, 3.2 V (VID (Voltage Identification) je ignorovaný), august

1997, 40 W

Napájanie:

3.1 V: 2.945 - 3.255 V

3.2 V: 3.1 - 3.3 V

3.3 V: 3.135 - 3.465 V

3.5 V: 3.325 - 3.675 V

Technológia: 0.35 mm biCMOS.

Násobiteľ: 2.5, 3, 3.5, alebo 4.

![]() Intel Pentium Pro P6L

CPU

Intel Pentium Pro P6L

CPU

Intel Pentium Pro P6 CPU bez L2 cache.

![]() Intel OverDrive P6T

CPU

Intel OverDrive P6T

CPU

P6 Micro architektúra Core (Pentium II Deschutes).

300 MHz: 23.8 W

333 MHz: 26.3 W

2.5 V interne, 3.3 V I/O.

Napájanie:

2.5 V: 2.375 - 2.625 V

3.3 V: 3.135 - 3.465 V

Púzdro: 387 vývodov PGA (Pin Grid Array) (Socket 8).

Technológia: 0.25 mm CMOS.

Integrácia: 7 500 000 tranzistorov.

IBM 6x86 CPU |

IBM 266x86-2V2100GB CPU: 50/100 MHz

IBM 266x86-2V2110GB CPU: 55/110 MHz

IBM 266x86-2V2120GB CPU: 60/120 MHz

IBM 266x86-2V2133GB CPU: 66/133 MHz

Marec 1996

Napájanie: 3.3 V.

CPUID: druh=0x5, model=0x3, krok=0.

IBM 6x86-P120+ CPU (IBM 266x86-2V2P120GE CPU): 50/100 MHz, 3.3 V core, I/O znáša 5V

IBM 6x86-P133+ CPU (IBM 266x86-2V2P133GE CPU): 55/110 MHz, 3.3 V core, I/O znáša 5V

IBM 6x86-P150+ CPU (IBM 266x86-2V2P150GE CPU): 60/120 MHz, 3.3 V core, I/O znáša 5V

IBM 6x86-P150+ CPU (IBM 266x86-2V7P150GE CPU): 60/120 MHz, 3.5 V core, I/O znáša 5V

IBM 6x86-P166+ CPU (IBM 266x86-2V2P166GE CPU): 66/133 MHz, 3.3 V core, I/O znáša 5V

IBM 6x86-P166+ CPU (IBM 266x86-2V7P166GE CPU): 66/133 MHz, 3.5 V core, I/O znáša 5V

IBM 6x86-P200+ CPU (IBM 266x86-2V7P200GE CPU): 75/150 MHz, 3.5 V core, I/O znáša

5V

November 1996

Púzdro: 296 vývodov SPGA (Pin Grid Array) (P54C socket kompatibilný).

DIR0 register: 0x31

DIR1 register: 0x1X / 0x2X

![]() IBM 6x86L CPU

IBM 6x86L CPU

Nízko odberová verzia (o 25 % redukovaná spotreba) IBM 6x86 CPU.

Napájanie: 2.8 V core, 3.3 V I/O, I/O znáša 5V.

IBM 6x86L-P120+ CPU: 50/100 MHz

IBM 6x86L-P133+ CPU: 55/100 MHz

IBM 6x86L-P150+ CPU: 60/120 MHz

IBM 6x86L-P166+ CPU (IBM 266x86L-2VAP150GB CPU): 66/133 MHz

IBM 6x86L-P200+ CPU (IBM 266x86L-2VAP150GB CPU): 75/150 MHz

Technológia: 5 vrstiev kovu, 0.44 mm IBM CMOS.

CPU používa dve napájacie napätia: 2.8 V pre core a 3.3 V pre I/O interface.

Púzdro: 296 vývodov SPGA (Pin Grid Array) (Socket 7 kompatibilný).

DIR0 register: 0x31

DIR1 register: 0x2X

Cyrix 6x86 CPU |

CPU triedy Pentium Pro (RISC s X86 prekladom). Pomalý FPU, výkon v plávajúcej

desatinnej čiarke je nízky.

V praktických testoch bežných aplikácií je rýchlejší ako Intel Pentium Pro (Cyrix

optimalizoval CPU pre 16 bit kód, Intel pre 32 bit kód).

Superzreťazený Superskalár:

2 celočíselné jednotky,

7 úrovní,

2 celočíselné jednotky,

FPU (Floating Point Unit).

Charakteristiky: premenovávanie registrov,

out-of-order vykonávanie,

dátovo��������������������������������������������������������������������������������������� závislé premiestňovanie,

multi-predikcia vetvenia,

špekulatívne vykonávanie.

TLB (Translation Look-aside Buffer): 128-entry L1, 8-entry victim.

pamäť cieľových adries skokov BTB (Branch Target Buffer): 256-entry, 4 asociatívne

sekcie, 512-entry branch history table.

16 kbyte unifikovaná cache: spätný zápis/write-through, 4 asociatívne sekcie,

dual-ported, MESI architektúra.

Pipelined burst-mode čítanie a zápis.

256 byte inštrukčná cache: plne asociatívna.

Multiprocesorová podpora: SLiC/MP, OpenPIC interrupt architektúra.

Vyberateľné násobenie 2x alebo 3x.

Management napájania:

SMM (System Management Mode),

Suspend Mode,

FPU auto-idle.

Cyrix 6x86 CPU: 3.3 V (C016) alebo 3.52 V (C028) core, I/O znáša 5V, from

revision 2.7 less power consumption.

40/80 MHz (Cyrix 6x86-PR90+ CPU): 3.3 V

50/100 MHz (Cyrix 6x86-P120+GP CPU): 3.3 V

55/110 MHz (Cyrix 6x86-P133+GP CPU): 3.3 V

60/120 MHz (Cyrix 6x86-P150+GP CPU): 3.3 alebo 3.52 V

66/133 MHz (Cyrix 6x86-P166+GP CPU): 3.3 alebo 3.52 V

75/150 MHz (Cyrix 6x86-PR200+ CPU): 3.52 V

Technológia: 0.65 mm CMOS.

Integrácia: 3 000 000 tranzistorov.

![]() Cyrix M1 CPU

Cyrix M1 CPU

Cyrix 6x86L CPU (low power): 2.8 V core, 3.3 V I/O.

50/100 MHz (Cyrix 6x86L-PR120+ CPU).

55/110 MHz (Cyrix 6x86L-PR133+ CPU).

60/120 MHz (Cyrix 6x86L-PR150+ CPU).

66/133 MHz (Cyrix 6x86L-PR166+ CPU).

75/150 MHz (Cyrix 6x86L-PR200+ CPU): Technológia: 0.44 mm CMOS.

Technológia: 0.5 mm CMOS.

Integrácia: 3 000 000 tranzistorov.

Púzdro:

296 vývodov PGA (Pin Grid Array) (Socket 7),

296 pin CPGA (Ceramic Pin Grid Array) (Socket 7).

Cyrix M1R CPU.

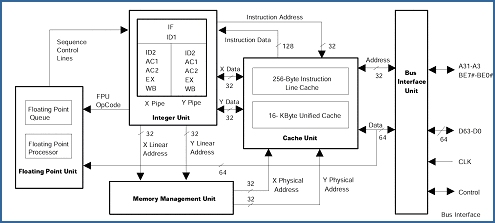

- Bloková schéma 6x86 Cyrix

NexGen Nx686 CPU |

CPU triedy Pentium Pro (RISC s X86 prekladom).

Cache: 16 kbyte pre inštrukcie, 32 kbyte pre data (Harvardská architektúra).

L2 cache controller.

180 MHz

Technológia: 5 vrstiev kovu, 0.35 mm IBM CMOS.

Integrácia: 6 000 000 tranzistorov.

Intel MMX technológia |

MMX projekt bol spustený v roku 1995 ako následník NSP iniciatívy (Native Signal

Processing) z roku 1994.

MMX (Matrix Math eXtensions, Multi-Media eXtensions) je určená pre audio, video a

komunikáciu. Technológia je tiež licencovaná AMD����������������������������������������������������������������������������������������� a Cyrixom.

KNI technológia (Katmai New Instructions, "MMX2"), pridáva ďalších 70

inštrukcií pre 3D aplikácie.

Vlastnosti:

MMX technológia poskytuje vyššiu výkonnosť počítačov

- 32 KB L1 procesorová cache, 2x väčšia ako P54C

- 20 % zvýšenie výkonu aplikácií

- 40 % rýchlejšie aplikácie optimalizované pre MMX CPU

MMX definuje 4 nové 64bitové dátové typy

- Packed byte (8 bytov zabalených do 64 bitov)

- Packed word (4 word zabalených do 64 bitov)

- Packed doubleword (2 zabalených do 64 bitov)

- Quadword (64 bitov)

MMX prináša osem 64 bitových registrov

- Floating-Point register

MMX pridáva novú inštrukčnú sadu

- 57 nových inštrukcií SIMD (Single-Instruction, Multiple-Data)

- inštrukcie zvyšujú výkonnosť aplikácií ako je Motion Video, Image Processing,

Audio Syntéza, 2D a 3D Grafika

- matematické, komparačné, konverzné, logické, rotácie, dátové prenosy, prázdne

MMX stavy

Použitá technika SIMD (Single Instruction Multiple Data)

- zvýšenie výkonu spracovaním mnohonásobných dát paralelne jednou inštrukciou

- spracuje štyri 16bitové (word) Audio dáta súčasne

- spracuje osem 8bitových (byte) Grafických dát súčasne

![]() Intel MMX Pentium P55C

CPU

Intel MMX Pentium P55C

CPU

· 16 kbyte inštrukčná cache,

· 16 kbyte data cache (Harvardská architektúra)

Január 1996

66/166 MHz: iCOMP 2.0 160

66/200 MHz: iCOMP 2.0 182

Jún 1997

66/233 MHz: iCOMP 2.0 203

66/266 MHz: (ukončená v roku 1997)

Voltáž: 2.8 V, 3.3 V I/O

Púzdro: 296 vývodov PPGA (Plastic Pin Grid Array) (Socket 7).

Technológia: 4 vrstvy kovu, 0.35 mm CMOS.

Integrácia: 4 500 000 tranzistorov.

![]() Intel Mobile Pentium/MMX

CPU

Intel Mobile Pentium/MMX

CPU

Dve MMX jednotky.

66/133 MHz

50/150 MHz

66/166 MHz

66/200 MHz

2.45 V, 3.3 V I/O.

66/166 MHz: január 1998, 2.9 W

66/200 MHz: september 1997, 3.4 W

66/233 MHz: september 1997, 3.9 W

66/266 MHz: 2.0 V, január 1998, 5.3 W

Integrácia: 4 500 000 tranzistorov.

1.8 V, 2.5 V I/O (Voltage Reduction Technológia).

Pracovný názov Tillamook.

Púzdro:

Mobile Module,

320 vývodov TCP (Tape Carrier Packaging).

Technológia: 5 vrstiev kovu, 0.25 mm CMOS.

![]() Intel Pentium/MMX

OverDrive CPU

Intel Pentium/MMX

OverDrive CPU

Pentium/MMX P54CTB OverDrive processor pre Intel Pentium CPUs.

2.8 V core (voltage regulátor), 3.3 V I/O.

50/125 MHz: pre 75, 100 MHz systémy

60/150 MHz: pre 90, 120 MHz systémy

66/166 MHz (BPODPMT66X166): pre 75 (to 50/125), 90 (to 60/150), 100, 133 MHz systémy

60/180 MHz (BPODPMT66X180): pre 75 (to 50/150), 90, 120, 150 MHz systémy, august 1997

66/200 MHz (BPODPMT66X200): pre 100, 133, 166 MHz Socket 7 systémy, august 1997

Napájanie: 3.3 V: 3.135 - 3.6 V.

Púzdro: 320 vývodov PGA (Pin Grid Array) (Socket 5/7).

Technológia: 4 vrstvy kovu, 0.35 mm CMOS.

Integrácia: 4 500 000 tranzistorov.